この記事で分かること

- アルミニウム配線の問題点は:銅より高い電気抵抗による信号遅延(RC遅延)、およびエレクトロマイグレーション耐性の低さによる断線リスクが主な問題点です。

- なぜ電気抵抗が高いのか:銅に比べて自由電子が結晶中を移動する際に、原子核や他の電子、格子振動(フォノン)などとの衝突が多いため、電気抵抗が高くなります。これにより、電子の流れが妨げられ、電流が流れにくくなります。

- 配線が微細なほど、抵抗が大きくなる理由:配線が細くなると、電流の通り道となる断面積が狭まります。これは、多数の自由電子が流れる際に、電子同士や配線の原子との衝突が頻繁に起こることを意味します。この「流れにくさ」が増すため、電気抵抗は断面積に反比例して増加します。

アルミニウム配線の問題点

半導体の重要性が増す中で、前工程装置は世界的に成長が続いています。

https://optronics-media.com/news/20250414/99245/

特に中国は米中対立もあり、大幅な投資増加が続いています。今後も先端技術を駆使した半導体の需要増加と従来技術による成熟プロセスともにその重要性は増加するとみられています。

今回は、配線形成、メタライゼーションに用いられるアルミニウム配線の問題点についての記事となります。

配線形成、メタライゼーションとは何か

半導体前工程における配線形成(メタライゼーション)とは、半導体チップ内で、トランジスタなどの素子同士を電気的に接続し、回路として機能させるために、金属の配線を形成する一連の技術とプロセスを指します。

- 金属配線層の形成:

- 材料: 主にアルミニウム (Al) や銅 (Cu) などの低抵抗金属、およびそれらの合金が用いられます。微細化が進むにつれて、より抵抗の低い銅への転換が進んでいます。また、配線材料とシリコンとの反応を防ぐためのバリアメタル(タングステン (W)、チタン (Ti) など)も使用されます。

- 成膜方法: 物理的成膜法 (PVD: 蒸着、スパッタリング) や化学的成膜法 (CVD: Chemical Vapor Deposition) などが用いられます。特に銅配線では、めっき法やダマシン法(後述)が活用されます。

- ビアホールの埋め込み: 複数の配線層を接続するために、層間絶縁膜に開けられたビアホール(穴)に金属を埋め込む技術です。タングステンなどが一般的に用いられます。

- 層間絶縁膜の形成: 配線層同士を電気的に絶縁するための膜を形成します。シリコン酸化膜が一般的ですが、信号伝達の遅延を抑えるために、より誘電率の低い(低誘電率)材料も研究されています。

- 平坦化技術: 多層配線を形成する際に生じる凹凸をなくし、表面を平坦にする技術です。CMP (Chemical Mechanical Polishing: 化学機械研磨) が代表的です。

- 配線信頼性評価技術: 形成された配線の電気的特性や信頼性(エレクトロマイグレーションなど)を評価する技術も含まれます。

なぜメタライゼーションが重要なのか?

半導体デバイスは、トランジスタなどの個々の素子が作られただけでは機能しません。それらの素子を適切に接続することで初めて、LSI(大規模集積回路)として複雑な演算やデータ処理が可能になります。メタライゼーションは、この「電気的な道筋」を作る極めて重要な工程であり、LSIの性能(高速性、低消費電力など)や信頼性に大きく影響します。

特に、近年における半導体の微細化と多層化の進展に伴い、配線の抵抗や寄生容量による信号遅延がLSIの高速化を妨げる大きな課題となっています。そのため、より低抵抗な材料の採用(例:AlからCuへ)、低誘電率の層間絶縁膜の開発、そしてそれらの材料を微細かつ高精度に加工する技術(ダマシン法など)が、メタライゼーション技術の進化を牽引しています。

半導体前工程の配線形成(メタライゼーション)は、トランジスタなどの素子同士を電気的に接続するため、金属膜を成膜・加工し、多層の電気配線を構築する技術です。これにより、LSIとして機能する回路が完成します。

アルミニウム配線の問題点は何か

アルミニウムは、加工の容易さ、コストの低さなどから、長らく半導体デバイスの配線材料として標準的に使用されてきました。

しかし、半導体の性能向上とともに、以下のようなアルミニウム配線の特徴が問題視されるようになっています。

高い電気抵抗

- 銅(Cu)に比べて電気抵抗が高いため、電流が流れにくい特性があります。

- これにより、配線を通る信号の速度が遅れる「RC遅延」が顕著になります。特に半導体の微細化が進むと、配線が細く長くなるため、この抵抗による信号遅延がデバイスの高速動作を妨げる主要な要因となります。

低いエレクトロマイグレーション耐性

- エレクトロマイグレーションとは、配線に高密度電流が流れ続けることで、電子の運動量が金属原子に伝わり、原子が移動して配線中にボイド(空孔)やヒロック(突起)を形成し、最終的に配線が断線する現象です。

- アルミニウムは銅に比べてこのエレクトロマイグレーションに対する耐性が低く、デバイスの信頼性や寿命に影響を与える可能性があります。特に微細化が進み、配線に流れる電流密度が高くなるほど、この問題は深刻になります。

低い熱伝導率

- 銅に比べて熱伝導率が低いため、デバイス内で発生する熱を効率的に外部に放出することが難しい場合があります。高集積化されたデバイスでは発熱が問題となるため、これは不利な点となります。

これらの問題点から、現在の最先端の半導体デバイスでは、より低抵抗でエレクトロマイグレーション耐性の高い銅配線が主流となっています。ただし、アルミニウム配線は加工の容易さやコストの低さという利点があるため、一部の用途や古いプロセスルールでは現在でも使われ続けています。

アルミニウム配線は、銅より高い電気抵抗による信号遅延(RC遅延)、およびエレクトロマイグレーション耐性の低さによる断線リスクが主な問題点です。これらの課題が、デバイスの高速化と信頼性向上を妨げます。

アルミニウムはなぜ銅よりも抵抗が高いのか

アルミニウムが銅よりも電気抵抗が高い主な理由は、両者の原子構造と結晶構造、およびそれらが自由電子の動きに与える影響の違いにあります。電気抵抗は、電流を運ぶ自由電子が、原子核や他の電子、あるいは結晶格子の振動(フォノン)などと衝突することで生じる「流れにくさ」の度合いを示すためです。

- 自由電子の動きやすさ(散乱の頻度):

- 銅 (Cu): 銅原子は、最外殻に1つの価電子を持ちます。この価電子は原子核からの引力が比較的弱く、結晶構造内を比較的自由に動き回ることができます。また、銅の結晶構造は、自由電子が原子と衝突する頻度がアルミニウムに比べて少ないとされています。このため、電子が効率的に移動しやすく、電気抵抗が低くなります。

- アルミニウム (Al): アルミニウム原子は、最外殻に3つの価電子を持ちます。原子核からの引力が銅の価電子に比べて強く、また、結晶構造や原子の振動(フォノン)によって自由電子が散乱される頻度が銅よりも高いと考えられています。この電子の散乱頻度の高さが、結果として電気抵抗の増加につながります。

- 原子間距離と電子の重なり:

- 金属の電気伝導は、原子の軌道が重なり合って形成される「バンド」の中を電子が移動することで起こります。このバンドの構造や、電子が占めるエネルギーレベル(フェルミ準位)が物質ごとに異なります。

- 銅はアルミニウムに比べて、電子が移動しやすいバンド構造を持っていると考えられます。

- フォノン散乱(熱による原子の振動):

- 金属の電気抵抗は温度が上昇すると増加します。これは、原子が熱によって激しく振動し(フォノン)、自由電子がその振動する原子に衝突する頻度が増加するためです。

- アルミニウムは銅に比べて、同じ温度条件下でのフォノン散乱が自由電子の動きに与える影響が大きい、あるいはフォノンの発生しやすい特性を持つ可能性があります。

簡潔に言うと、銅の方がアルミニウムよりも自由電子が結晶中を「スムーズに、妨げられずに」移動できる構造を持っているため、電気抵抗が低く、優れた導体となります。

一般的な抵抗率の目安として、

- 銅:約 1.68×10−8Ω⋅m

- アルミニウム:約 2.65×10−8Ω⋅m

となり、銅の方が低い抵抗率を示すことが分かります。

アルミニウムは、銅に比べて自由電子が結晶中を移動する際に、原子核や他の電子、格子振動(フォノン)などとの衝突が多いため、電気抵抗が高くなります。これにより、電子の流れが妨げられ、電流が流れにくくなります。

配線抵抗による信号遅延はなぜ起きるのか

半導体チップ内部の配線で信号遅延が発生する主な原因は、配線が持っている抵抗(R)と、配線と周辺の配線や基板との間に生じる容量(C)が組み合わさることで発生するRC遅延です。

RC遅延のメカニズム

配線は、電流が流れる導体ですが、完全なゼロ抵抗ではありません。また、配線同士や、配線と下の基板や上の層間絶縁膜との間には、非常に近い距離に導体と絶縁体が存在するため、コンデンサ(キャパシタンス)が形成されます。

- 抵抗による電圧降下と充電時間の発生:

- 信号が配線を伝わる際、配線の持つ抵抗によって電圧降下が生じます。

- 信号が変化する(例えば、0Vから5Vへ立ち上がる)とき、配線に接続された次の素子や、配線自身が持つ容量を充電する必要があります。この充電には時間がかかります。

- 配線抵抗が高いほど、電流が流れにくくなり、この充電に要する時間が長くなります。

- 容量による電荷蓄積:

- 配線に容量が存在するということは、その容量に電荷を蓄えたり、放出したりする必要があるということです。

- 信号が立ち上がる際には、配線容量が充電されることで、その容量に電流が流れ込みます。この電流は、本来次の素子へ伝わるべき信号電流の一部を消費してしまいます。

- 配線容量が大きいほど、より多くの電荷を蓄える必要があるため、充電時間が長くなり、信号が目標電圧に到達するまでに時間がかかります。

例えるなら…

- 抵抗: 細くて長いホース(配線)をイメージしてください。水の抵抗(抵抗)が大きいため、水(信号)が勢いよく流れず、目的地に到達するのに時間がかかります。

- 容量: ホースの途中に、水を一時的に溜めてしまう小さな水槽(容量)があるようなものです。この水槽が満たされないと、次の目的地へ水が流れていきません。水槽が大きいほど、満たすのに時間がかかります。

信号が配線抵抗と配線容量を通過する際、RC時定数(RとCの積)に応じた遅延が発生します。この時定数が大きいほど、信号の立ち上がりや立ち下がりが鈍くなり、結果として信号が次の回路に到達するまでの時間が長くなる、つまり信号遅延が発生します。

微細化とRC遅延

半導体デバイスの微細化が進むと、以下の理由でRC遅延がさらに大きな問題となります。

- 配線の断面積の減少: 配線が細くなるため、抵抗が増加します。

- 配線間隔の縮小: 配線同士が近くなるため、配線間の容量が増加します。

- 多層化: 配線層が増えることで、全体の配線長が長くなり、抵抗と容量の総量が増加します。

これらの要因により、微細化されたLSIでは配線遅延がゲート遅延(トランジスタ自体の動作遅延)を上回るようになり、デバイスの高速動作を妨げる主要な課題となっています。

対策

RC遅延を低減するためには、主に以下の対策が取られます。

- 配線構造の最適化: 配線幅の最適化、リピーターセルの挿入(長い配線を途中で増幅器で区切る)など。

- 低抵抗材料の採用: アルミニウムから銅への移行(銅の方が抵抗が低い)。

- 低誘電率(Low-k)材料の採用: 層間絶縁膜の誘電率を下げて、配線間容量を低減する。

配線抵抗による信号遅延は、配線の持つ抵抗(R)と容量(C)が組み合わさり、RC時定数が発生するためです。信号が配線抵抗を流れて容量を充電するのに時間がかかり、信号が目標電圧に到達するまでに遅延が生じます。微細化でRとCが増加し問題が顕在化しています。

なぜ配線が微細化すると抵抗が増加するのか

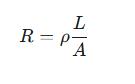

配線が細くなると抵抗が増加するのは、電気抵抗の基本的な法則に基づいています。導体の電気抵抗 R は、以下の式で表されます。

- R は電気抵抗 (Ω)

- ρ (ロー) は抵抗率 (Ω·m) – 材料固有の値で、電気の流れにくさを示す

- L は導体の長さ (m)

- A は導体の断面積 (m²)

この式から分かるように、電気抵抗 R は導体の断面積 A に反比例します。

なぜ断面積が小さくなると抵抗が増えるのか?

例えるなら、水の流れを考えてみると分かりやすいです。

- 太いホース(広い断面積): 水がスムーズに大量に流れることができます。抵抗が小さい状態です。

- 細いホース(狭い断面積): 同じ量の水を流そうとすると、水は抵抗を受けて流れにくくなります。これが抵抗が大きい状態です。

電気の場合も同様で、導体の断面積が小さくなるということは、電流を運ぶ自由電子が通過できる「道幅」が狭くなることを意味します。道幅が狭いと、自由電子が原子や他の電子と衝突する頻度が高まり、その結果、電子の流れが妨げられやすくなります。

半導体配線では、微細化によって配線幅がnm(ナノメートル)オーダーになると、単に断面積が小さくなるだけでなく、以下のような影響も抵抗増加に寄与します。

- 表面・界面散乱の増加: 配線が非常に細くなると、自由電子が配線の表面や、配線と層間絶縁膜との界面に衝突する機会が増えます。この衝突も電子の移動を妨げる要因となり、抵抗が増加します。

- 粒界散乱の増加: 配線材料が多数の結晶粒の集合体である場合、結晶粒の境界(粒界)でも電子が散乱されます。配線が細くなると、相対的に粒界の数や影響が大きくなり、抵抗が増加する可能性があります。

このように、配線が細くなると、自由電子の通り道が狭まることに加えて、表面や粒界での散乱が増えることで、全体としての電気抵抗が大きく増加するのです。これが、微細化された半導体デバイスにおけるRC遅延の主要な原因の一つとなっています。

配線が細くなると、電流の通り道となる断面積が狭まります。これは、多数の自由電子が流れる際に、電子同士や配線の原子との衝突が頻繁に起こることを意味します。この「流れにくさ」が増すため、電気抵抗は断面積に反比例して増加します。

コメント